My research is focused towards emerging spintronic devices for low-power and enhanced security. In particular, I am interested in the following topics:

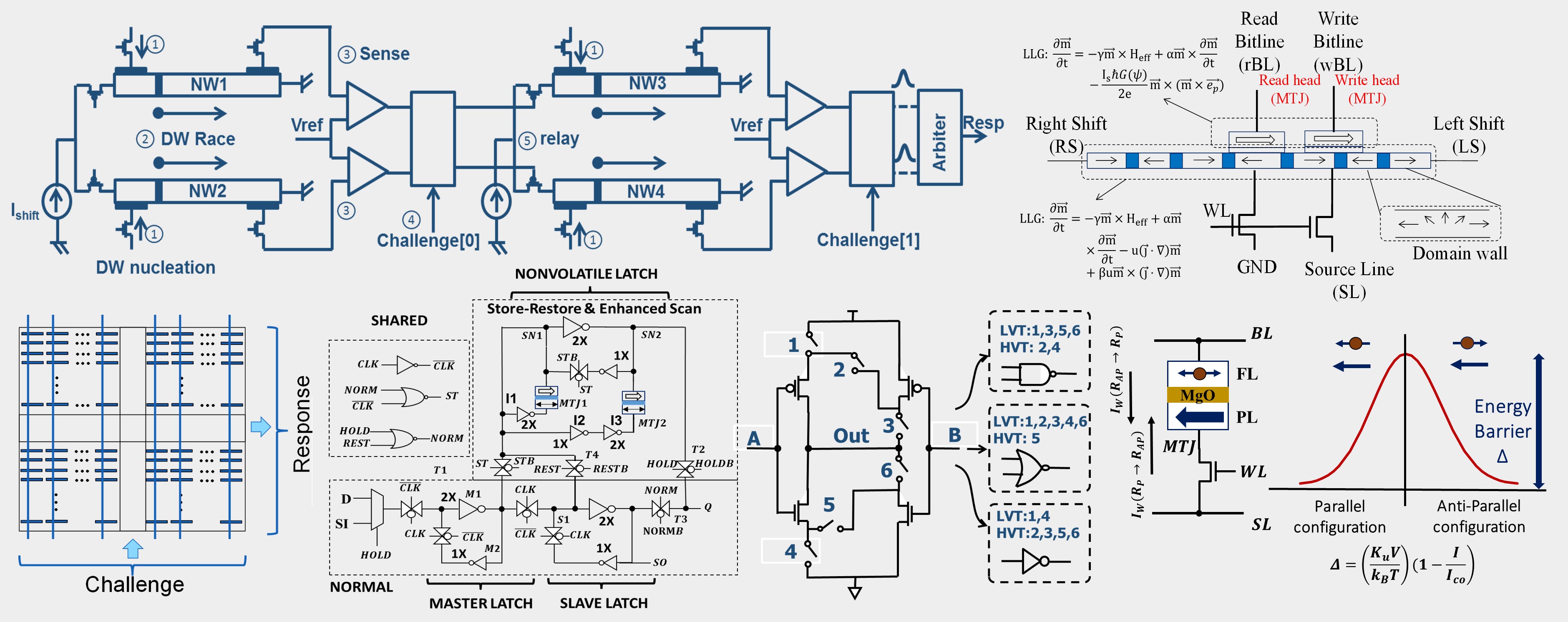

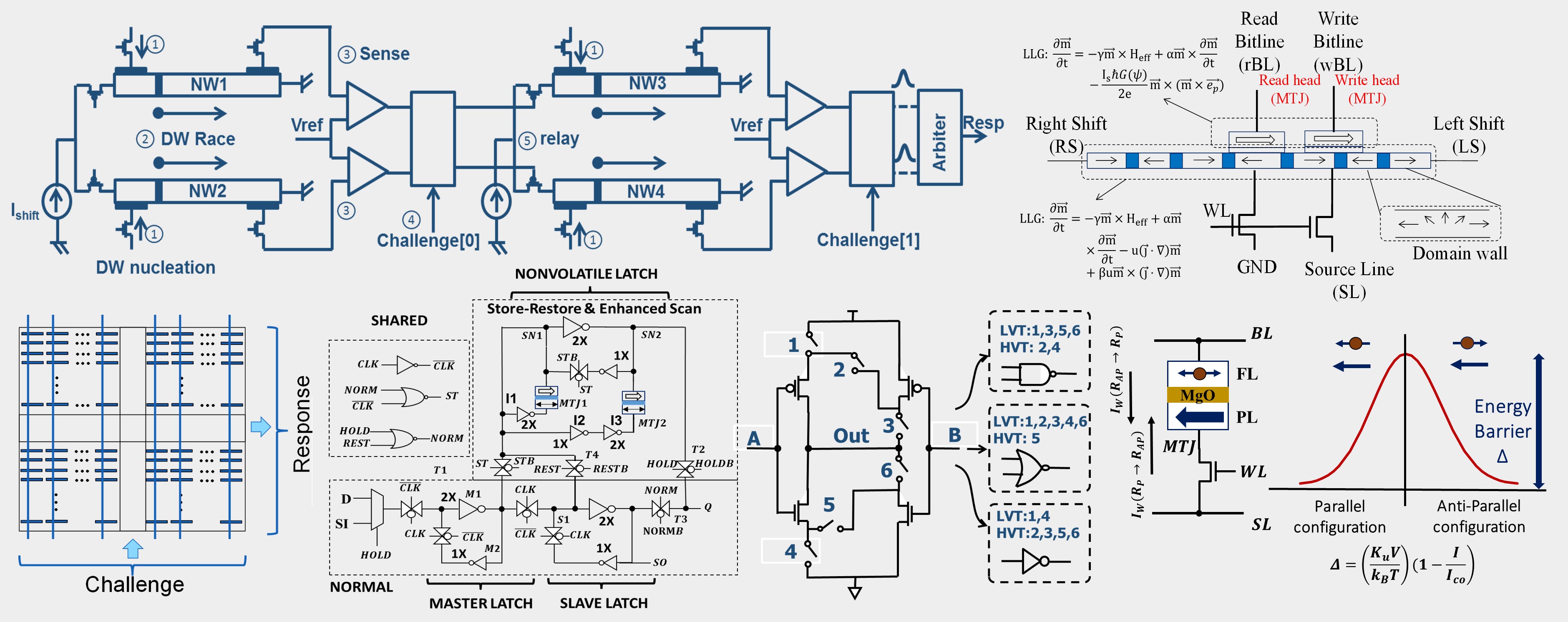

Security using spintronics: In this project I am investigating the prospects and challenges of spintronic devices towards hardware security

Investigating the emerging threat models, detection and protection mechanisms associated with spintronic memories. [J4, J5, C4, C7, C9].

Exploit the randomness in Domain Wall dynamics for security primitives such as Physically Unclonable Functions. [J1, J4, C2].

Aside from this, I am also investigating the use of multi-threshold based CMOS logic, aimed at camouflaging ICs against cloning. [C5, C6].

Additionally, I have explored the side channel vulnerabilities of STTRAM memory and have provided some low-overhead countermeasures. [C8].

Application of spintronics: In this project I am investigating the state retentive sequentials and non-volatile cache.

Modeling, circuit design and micro-architectures for robust, low-power and energy efficient Domain wall memories (DWM). [J1, J2, C1, C3].

Reliability and retention analysis of spin transfer torque RAM (STTRAM) memory: In this project I am modeling STTRAM lifetime and retention and developing algorithms for test time improvement. [J5]

Camouflaging of circuit design using threshold defined switches: In this project I investigate the potential security application of threshold voltage defined switches in circuit camouflaging.

Investigate the tradeoff between area and performance overhead against reverse engineering effort [C5, C6].

Look at the best case implementation of camouflage gates, quantified over circuit node’s observability and controllability metrics [P6].

Integrity and authentication of Printed Circuit Boards [PCB]: In this project I investigate some countermeasures to mitigate PCB cloning, and also put forth benchmarks to test PCB security [P5].

I have also worked on PCB based PUFs for board authentication. [P9].